### NORTHWESTERN UNIVERSITY

## Analysis, Characterization and Design of Data Mining Applications and Applications to Computer Architecture

## A DISSERTATION

## SUBMITTED TO THE GRADUATE SCHOOL IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

for the degree

## DOCTOR OF PHILOSOPHY

Field of Electrical and Computer Engineering

By

Berkin Ozisikyilmaz

EVANSTON, ILLINOIS

December 2009

© Copyright by **Berkin Ozisikyilmaz** 2009

All Rights Reserved

### ABSTRACT

Analysis, Characterization and Design of Data Mining Applications and Applications to Computer Architecture

#### Berkin Ozisikyilmaz

Data mining is the process of automatically finding implicit, previously unknown, and potentially useful information from large volumes of data. Data mining algorithms have become vital to researchers in science, medicine, business, and security domains. Recent advances in data extraction techniques have resulted in tremendous increase in the input data size of data mining applications. Data mining systems, on the other hand, have been unable to maintain the same rate of growth. Therefore, there is an increasing need to understand the bottlenecks associated with the execution of these applications in modern architectures.

In our work, we present MineBench, a publicly available benchmark suite containing fifteen representative data mining applications belonging to various categories. First, we highlight the uniqueness of data mining applications. Subsequently, we evaluate the MineBench applications on an 8-way shared memory (SMP) machine and analyze important performance characteristics. Our results show that data mining workloads are quite different than those of other common workloads. Therefore, there is a need to specifically address the limitations of accelerating them. We propose some initial designs and results for accelerating them using programmable hardware.

After the analysis of the data mining applications, we have started using them to solve some of the computer architecture problems. In a study, we have used linear regression and neural network models in the area of design space exploration area. Design space exploration is a tedious, complex and time consuming task of determining the optimal solution to a problem. Our methodology relies on extracting the performance of a small fraction of the machines to create a model and use it to predict the performance of any machine. We have also shown using a subset of the processors available for purchase; we can create a very accurate model presenting the relation between the processor properties and its price. In another study, we try to achieve the ultimate goal of computer system design, i.e. satisfy the end-users, using data mining methods. We aim at leveraging the variation in user expectations and satisfaction relative to the actual hardware performance to develop more efficient architectures that are customized to end-users.

#### Acknowledgements

I express my deep gratitude to my advisors, Prof. Alok Choudhary, and co-advisor Prof. Gokhan Memik for their constant guidance and extensive feedback. My gratitude and appreciation also goes to Prof. Wei-keng Liao for serving as one of the committee member of my thesis and for his valuable feedback. This work was supported in part by National Science Foundation (NSF) under grants NGS CNS-0406341, IIS-0536994/002, CNS-0551639, CCF-0621443, CCF-0546278, and NSF/CARP ST-HEC program under grant CCF-0444405, and in part by the Department of Energys (DOE) SCiDAC program (Scientific Data Management Center), number DE-FC02-01ER25485, DOE grants DE-FG02-05ER25683, and DE-FG02-05ER25691, and in part by Intel Corporation.

I would like to thank my lab mates at *Center for Ultra Scale Computing and Information Security* and *Microarchitecture Research Lab* at Northwestern University for teaming with me in realizing my research goals. I would also like to thank my friends for those lighter moments during my doctoral study at Northwestern.

Last but not least, I am very grateful to my mother Neyran Uzkan and father Ziya Ozisikyilmaz for their encouragement and moral support through all these years in my life, and also for providing me the best possible level of education and knowledge. Also, I would like to thank my brother Ozgun Ozisikyilmaz for his continuous encouragement.

## Table of Contents

| ABSTRACT                                                               | 3  |

|------------------------------------------------------------------------|----|

| Acknowledgements                                                       | 5  |

| List of Tables                                                         | 9  |

| List of Figures                                                        | 11 |

| Chapter 1. Introduction                                                | 15 |

| 1.1. Contributions                                                     | 18 |

| 1.2. Organization                                                      | 19 |

| Chapter 2. Literature Survey                                           | 21 |

| 2.1. Analysis, Characterization and Design of Data Mining Applications | 21 |

| 2.2. Applications of Data Mining to Computer Architecture              | 24 |

| Chapter 3. MineBench                                                   | 27 |

| 3.1. Need for a New Benchmarking Suite and Uniqueness                  | 28 |

| 3.2. Benchmark Suite Overview                                          | 31 |

| Chapter 4. Architectural Characterization                              | 41 |

| 4.1. Execution Time and Scalability                                    | 41 |

| 4.2. Memory Hierarchy Behavior                                         | 45 |

|         |                                                                      | 7   |

|---------|----------------------------------------------------------------------|-----|

| 4.3.    | Instruction Efficiency                                               | 47  |

| Chapte  | er 5. Hardware Acceleration of Data Mining Applications              | 50  |

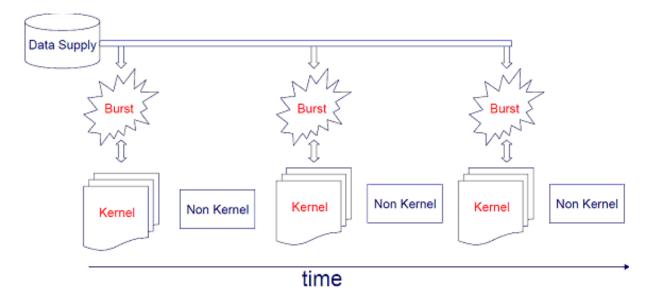

| 5.1.    | Kernels                                                              | 50  |

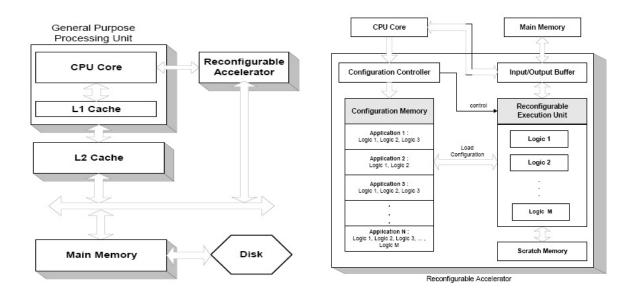

| 5.2.    | Case Studies using Reconfigurable Accelerator                        | 54  |

| 5.3.    | Case Studies using Graphical Processing Unit as Hardware Accelerator | 59  |

| Classic |                                                                      | 66  |

| Chapte  |                                                                      | 66  |

| 6.1.    | Fixed Point Arithmetic                                               | 67  |

| 6.2.    | Selected Applications                                                | 68  |

| 6.3.    | Conversion and Results                                               | 69  |

| Chapte  | er 7. Data Mining Models to Predict Performance of Computer System   |     |

| -       | Design Alternatives                                                  | 75  |

| 7.1.    | Motivation                                                           | 75  |

| 7.2.    | Overview of Predictive Modeling                                      | 77  |

| 7.3.    | Predictive Models                                                    | 80  |

| 7.4.    | Prediction Results                                                   | 87  |

|         |                                                                      |     |

| Chapte  | er 8. Profit-Aware Cache Architectures                               | 107 |

| 8.1.    | Speed-binning                                                        | 107 |

| 8.2.    | Substitute Cache Scheme                                              | 109 |

| 8.3.    | Price Modeling                                                       | 110 |

| 8.4.    | Revenue Estimation and Profit                                        | 113 |

| Chapte  | r 9. Learning and Leveraging the Relationship between Architecture-Level |     |

|---------|--------------------------------------------------------------------------|-----|

|         | Measurements and Individual User Satisfaction                            | 117 |

| 9.1.    | Motivation                                                               | 117 |

| 9.2.    | Hardware Performance Counters                                            | 119 |

| 9.3.    | Experimental Setup                                                       | 120 |

| 9.4.    | Relation between user Satisfaction and Hardware Performance Counters     | 120 |

| 9.5.    | Predictive User-Aware Power Management                                   | 123 |

| 9.6.    | Predictive Model Building                                                | 124 |

| 9.7.    | Experimental Results                                                     | 127 |

| Chapte  | r 10. Conclusion                                                         | 131 |

| 10.1.   | Future Work                                                              | 133 |

| Referer | nces                                                                     | 135 |

| Append  | dix A. Training Neural Networks                                          | 146 |

| Append  | lix B. Correlation factors for user satisfaction                         | 150 |

8

## List of Tables

| 3.1 | Overview of the MineBench data mining benchmark suite                                                | 27 |

|-----|------------------------------------------------------------------------------------------------------|----|

| 3.2 | Comparison of data mining application with other benchmark applications                              | 30 |

| 4.1 | MineBench executable profiles                                                                        | 42 |

| 5.1 | Top three kernels of applications in MineBench and their contribution<br>to the total execution time | 52 |

| 5.2 | Basic statistical Kernels                                                                            | 63 |

| 6.1 | Overview of the MineBench applications analyzed                                                      | 69 |

| 6.2 | Timing and Speedup for K-means                                                                       | 70 |

| 6.3 | Relative Percentage Error for K-means Membership                                                     | 70 |

| 6.4 | Timing and Speedup for Fuzzy K-means                                                                 | 72 |

| 6.5 | Relative Percentage Error for Fuzzy K-means Membership                                               | 72 |

| 6.6 | Timing and Speedup for Utility Mining                                                                | 73 |

| 6.7 | Average Relative Error for the total utility values of the points for                                | 79 |

|     | various support values                                                                               | 73 |

| 6.8 | Number of Itemsets satisfying the Utility criteria for various support |     |

|-----|------------------------------------------------------------------------|-----|

|     | values                                                                 | 74  |

| 7.1 | Data statistics obtained from SPEC announcements                       | 89  |

| 7.2 | Data set obtained from SPEC announcements (32 dimensions/columns)      | 90  |

| 7.3 | Configurations used in microprocessor study                            | 92  |

| 7.4 | Data statistics obtained from SPEC benchmark simulations               | 92  |

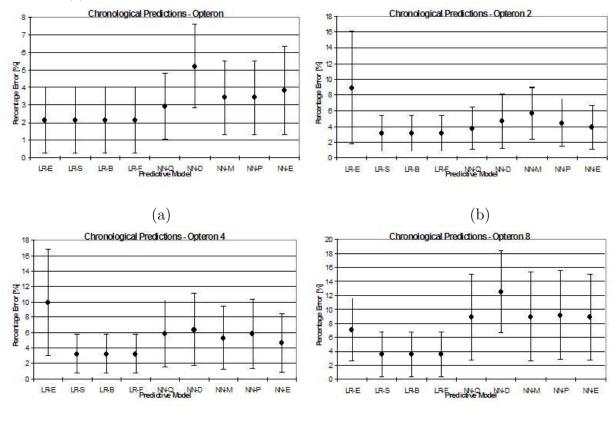

| 7.5 | Average accuracy results from SPEC published results                   | 104 |

| 7.6 | The best accuracy achieved for single processor and multiprocessor     |     |

|     | chronological design space exploration and the model that achieves     |     |

|     | this accuracy                                                          | 105 |

| 7.7 | Average accuracy results from SPEC simulations                         | 106 |

| 8.1 | Increase in revenue for various cache-architectures                    | 115 |

| 9.1 | Hardware counters we use in our experiments                            | 120 |

| B.1 | Correlation between the hardware performance counters and user         |     |

|     | satisfaction                                                           | 150 |

# List of Figures

| 1.1 | Data mining applications in MineBench                                                                                              |    |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| 3.1 | Classification of data mining, SPEC INT, SPEC FP, MediaBench<br>and TPC-H benchmark applications based on their characteristics. A |    |  |  |

|     | K-means based clustering algorithm was used for this classification.                                                               |    |  |  |

|     | Data mining applications tend to form unique clusters.                                                                             | 30 |  |  |

| 4.1 | Speedups for the MineBench applications                                                                                            | 43 |  |  |

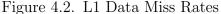

| 4.2 | L1 Data Miss Rates                                                                                                                 | 45 |  |  |

| 4.3 | L2 Cache Miss Rates                                                                                                                | 45 |  |  |

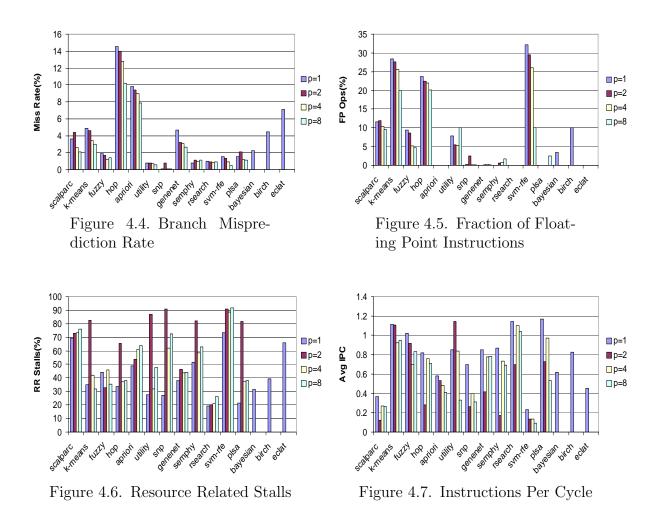

| 4.4 | Branch Misprediction Rate                                                                                                          | 48 |  |  |

| 4.5 | Fraction of Floating Point Instructions                                                                                            | 48 |  |  |

| 4.6 | Resource Related Stalls                                                                                                            | 48 |  |  |

| 4.7 | Instructions Per Cycle                                                                                                             | 48 |  |  |

| 5.1 | Speedups for the MineBench applications                                                                                            | 51 |  |  |

| 5.2 | Data Mining Systems Architecture                                                                                                   | 53 |  |  |

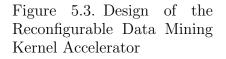

| 5.3 | Design of the Reconfigurable Data Mining Kernel Accelerator                                                                        | 53 |  |  |

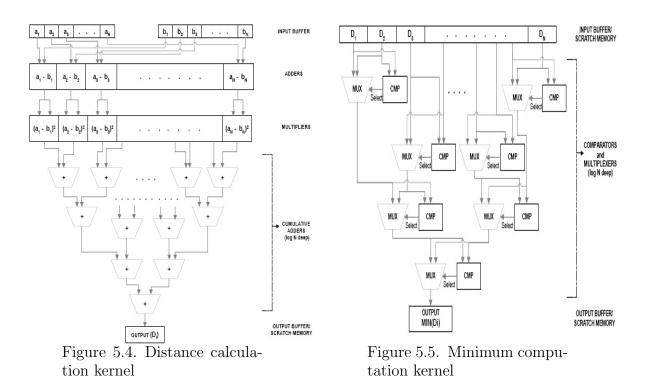

| 5.4 | Distance calculation kernel                                                                                                        | 55 |  |  |

| 5.5 | Minimum computation kernel                                                                                                                          | 55 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

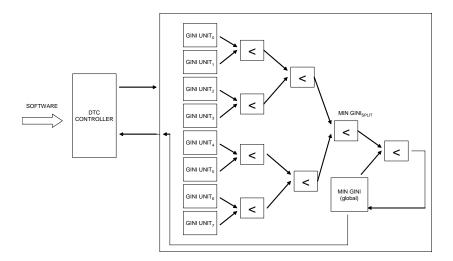

| 5.6 | Architecture for Decision Tree Classification                                                                                                       | 59 |

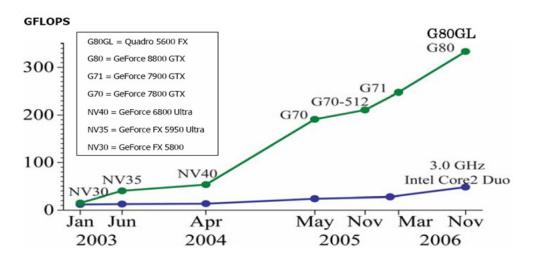

| 5.7 | GPU vs. CPU Floating-Point Performance                                                                                                              | 60 |

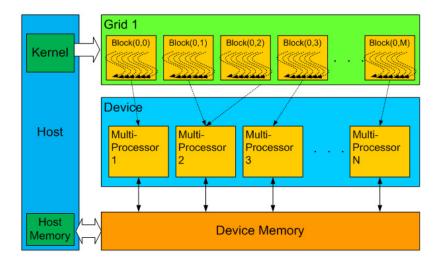

| 5.8 | GeForce 8800 GPU Hardware showing Thread Batching                                                                                                   | 61 |

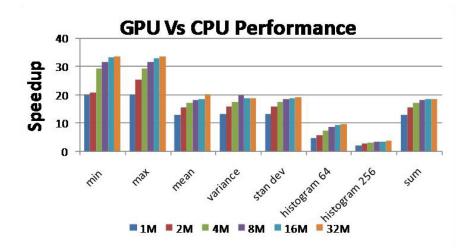

| 5.9 | Performance results for basic statistical functions for different input size                                                                        | 64 |

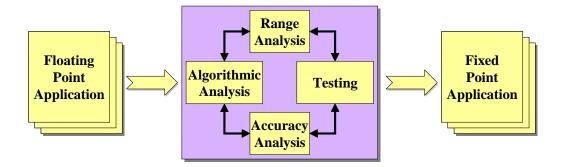

| 6.1 | Fixed Point Conversion Methodology                                                                                                                  | 67 |

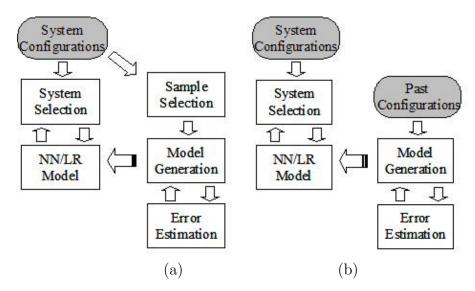

| 7.1 | Overview of design space exploration using predictive modeling: (a)<br>sampled design space exploration and (b) chronological predictive<br>models. | 79 |

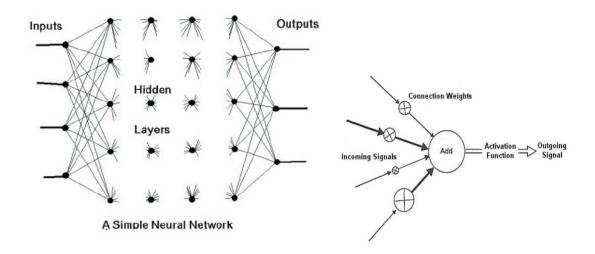

| 7.2 | Multiple Layered ANN                                                                                                                                | 84 |

| 7.3 | An example of a hidden unit                                                                                                                         | 84 |

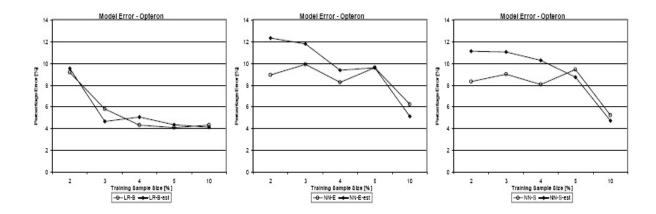

| 7.4 | Estimated vs. true error rates for Opteron based systems                                                                                            | 93 |

| 7.5 | Estimated vs. true error rates for Opteron 2 based systems                                                                                          | 94 |

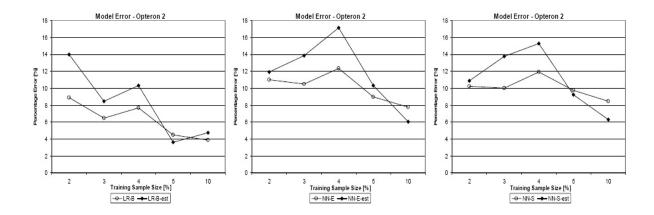

| 7.6 | Estimated vs. true error rates for Pentium 4 based systems                                                                                          | 95 |

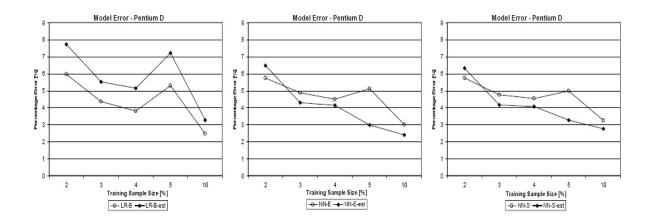

| 7.7 | Estimated vs. true error rates for Pentium D based systems                                                                                          | 96 |

| 7.8 | Estimated vs. true error rates for Xeon based systems                                                                                               | 96 |

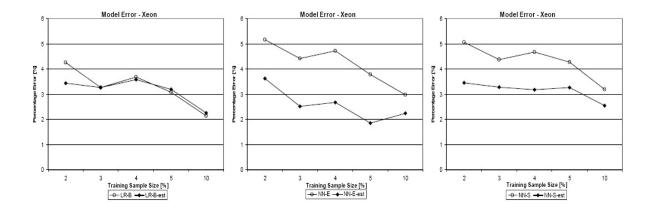

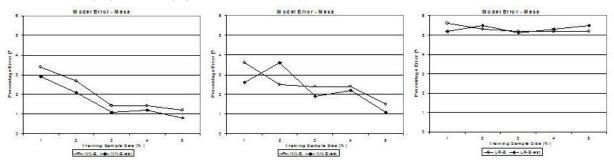

| 7.9 | Chronological predictions for Xeon (a), Pentium 4 (b), Pentium D (c) based systems                                                                  | 99 |

|     |                                                                                                                                                     | -  |

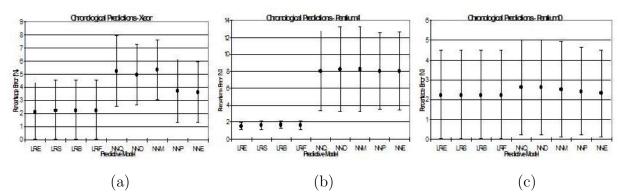

| 7.10 | Chronological predictions for Opteron based multiprocessor systems:     |     |  |

|------|-------------------------------------------------------------------------|-----|--|

|      | (a) one processor, (b) two processors, (c) four processors, and (d)     |     |  |

|      | eight processors                                                        | 99  |  |

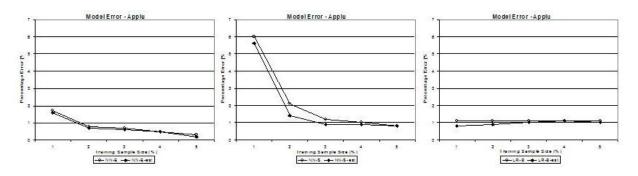

| 7.11 | Estimated vs. true error rates for Applu application: NN-E (L), NN-S    | 3   |  |

|      | (M), LR-B (R)                                                           | 102 |  |

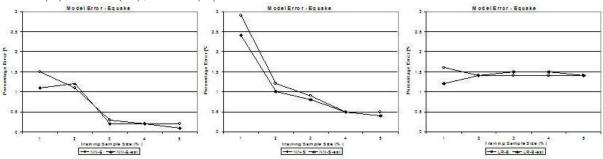

| 7.12 | Estimated vs. true error rates for Equake application: NN-E (L),        |     |  |

|      | NN-S (M), LR-B (R)                                                      | 102 |  |

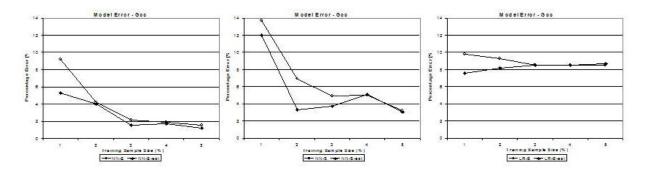

| 7.13 | Estimated vs. true error rates for Gcc application: NN-E (L), NN-S      |     |  |

|      | (M), LR-B (R)                                                           | 103 |  |

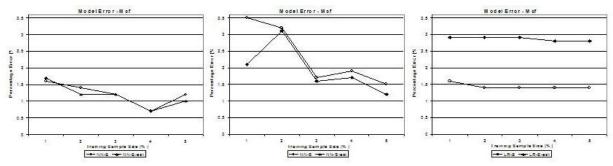

| 7.14 | Estimated vs. true error rates for Mcf application: NN-E (L), NN-S      |     |  |

|      | (M), LR-B (R)                                                           | 103 |  |

| 7.15 | Estimated vs. true error rates for Mesa application: NN-E (L), NN-S     | 5   |  |

|      | (M), LR-B (R)                                                           | 103 |  |

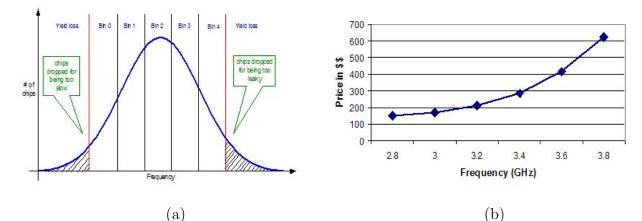

| 8.1  | (a) Frequency binning in modern microprocessors. (b) Price vs.          |     |  |

|      | frequency of Intel Pentium 4 family                                     | 108 |  |

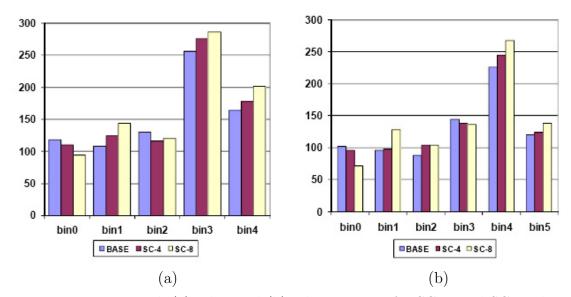

| 8.2  | Binning with (a) 5-bin and (b) 6-bin strategy for SC- 4 and SC-8        |     |  |

|      | schemes                                                                 | 114 |  |

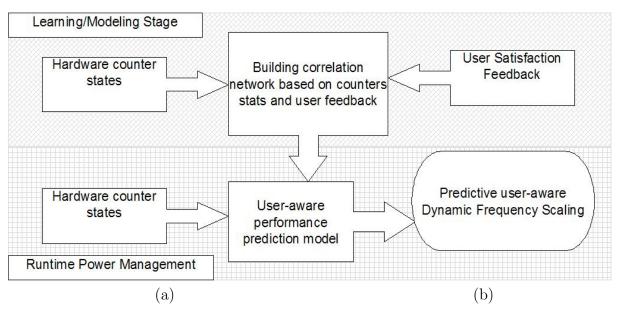

| 9.1  | Framework of the predictive user-aware power management                 | 124 |  |

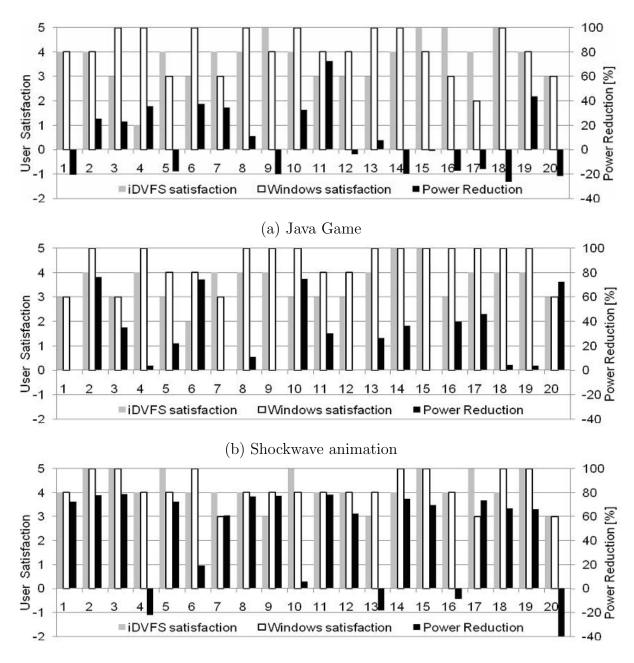

| 9.2  | User satisfaction and dynamic power reduction for iDVFS over            |     |  |

|      | Windows XP DVFS scheme. In the graphs, the horizontal axes reflec       | t   |  |

|      | the individual users in the study, while the left vertical axes reflect |     |  |

| the reported satisfaction for iDVFS and Windows XP DVFS, and the     | è   |

|----------------------------------------------------------------------|-----|

| right vertical axes report the percentage reduction in dynamic power |     |

| of iDVFS compared to Windows XP DVFS                                 | 126 |

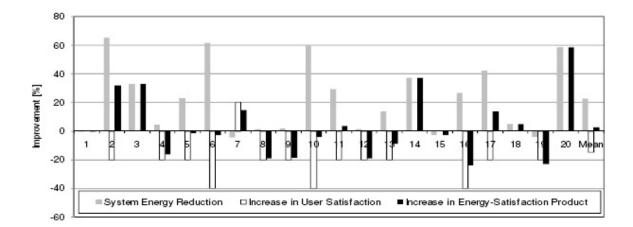

| Improvement in energy consumption, user satisfaction, and            |     |

| energy-satisfaction product for the Shockwave application            | 129 |

9.3

#### CHAPTER 1

#### Introduction

Latest trends indicate beginning of a new era in data analysis and information extraction. Todays connect anytime and anywhere society based on the use of digital technologies is fueling data growth, which is doubling every two years (if not faster), akin to "Moore's law for data" [52]. This growth is transforming the way business, science and digital technology based world function. Various businesses are collecting vast amounts of data to make forecasts and intelligent decisions about future directions. The worlds largest commercial databases are over the 100TB mark, whereas the database sizes on hybrid systems are approaching the PB mark [111]. Some of these large databases are growing by a factor of 20 every year. In addition, millions of users on the Internet are making data available for others to access. Countless libraries and databases containing photographs, movies, songs, etc. are available to a common user. In addition to the increasing amount of available data, other factors make the problem of information extraction particularly complicated. First, users ask for more information to be extracted from their data sets, which requires increasingly complicated algorithms. Second, in many cases, the analysis needs to be done in real time to reap the actual benefits. For instance, a security expert would strive for real-time analysis of the streaming video and audio data in conjunction. Managing and performing run-time analysis on such data sets is appearing to be the next big challenge in computing.

For these reasons, there is an increasing need for automated applications and tools to extract the required information and to locate the necessary data objects. Data mining is the process of automated extraction of predictive information from large datasets. It involves algorithms and computations from different domains such as mathematics, machine learning, statistics, and databases. Data mining is becoming an essential tool in various fields including business (marketing, fraud detection, credit scoring, decision systems), science (climate modeling, astrophysics, biotechnology), and others such as search engines, security, and video analysis.

An important perspective on applications and workloads for future data intensive applications is Recognition, Mining, and Synthesis [19]. In this perspective, applications are divided into three groups; namely, Recognition, Mining and Synthesis (RMS). Recognition (R) is the capability to recognize or learn interesting patterns or a model within large amounts of data for a specific application domain. Patterns may be of interest in heterogeneous applications such as video surveillance, credit card and banking transactions, security related databases with government agencies etc.. Mining (M) is the capability to analyze these large amounts of data for important objects or events, knowledge or actionable items. Depending on the type of applications domain, different characteristics and outcomes dominate. For example, for intrusion detection or on-line surveillance, the ability to continuously mine real-time streams of data is very important, whereas for a health-care diagnosis and personalized medicine application, accurate prediction of disease and treatment based on historical data and models would be important. Recognition and Mining are closely related. Finally, Synthesis (S) refers to applications that can use these models and data to create virtual or artificial environments to mimic the patterns

that are discovered. Alternatively, these models and outcomes may be incorporated into operational systems of businesses, such as recommendation systems for health-care or marketing. Clearly, these characteristics are quite different from traditional IT applications, which are targeted by current hardware and software systems. Just as graphics and multimedia applications have had tremendous impact on processors and systems, these data intensive data mining applications are expected to have tremendous impact on future systems.

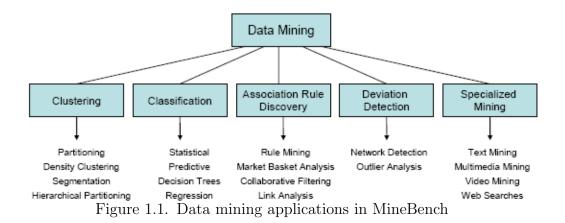

Data mining applications are classified based on the methodology used for data analysis and information learning. A typical data mining taxonomy is shown in Figure 1.1 [47]. Note that the same data can be analyzed using different techniques. For instance, a mobile phone company can use clustering mechanisms to identify the current traffic distribution before reassigning base stations. On the other hand, an analyst would use predictive methods to identify potential customers for a new mobile phone service plan. In addition, a data mining application usually consists of sequential execution of a number of tasks/algorithms. For example, a data set might first be pre-processed (e.g., sorted), then clustered, and then analyzed using association rule discovery. Recently, more and more computer architecture researchers are borrowing machine learning / data mining techniques to attack problems in real-world computer systems: such as modeling microprocessors [61] and cache structures, power and performance modeling of applications [66, 115], reduced workloads and traces to decrease simulation time [32, 56]. The motivation is simple: building empirical models based on statistical pattern recognition, data mining, probabilistic reasoning and other machine learning methods promises to help us cope with the challenges of scale and complexity of current and future systems. In the following sections, we present some other applications of data mining algorithms in computer architecture.

#### 1.1. Contributions

In this thesis, we do analysis and performance characterization of data mining applications and then show how we can borrow ideas from this domain to tackle and solve computer architecture related problems. In particular, we make following contributions:

- We have shown that data creation and collection rates are growing exponentially. Data mining is becoming an important tool used by researchers in many domains. Previously, there hasn't been a mechanism to review data mining algorithms and the systems that run them. Therefore we have introduced, NU-MineBench, a data mining benchmark suite.

- Initial analysis has shown that data mining applications have significantly different characteristics than previously available benchmarks such as SPEC, i.e.

data mining applications are both data and computation intensive. Since current architectures are designed for the older workloads, we have done detailed architectural characterization to find the needs of data mining applications.

- We have proposed how we can use reconfigurable and reprogrammable hardwares to overcome some of the bottlenecks identified in the characterization phase. These results indicate that significant performance improvement can be achieved. Also we have shown that conversion of floating point operations to fixed point operations on these reconfigurable architectures can further increase the performance.

- The problems in the computer architecture area are very large, complex and time consuming to solve. We have presented how we can use some basic data mining methods and applied them to these problems. Specifically, we have shown that the efforts needed to solve the design space exploration problem can be reduced as much as 100× without causing significant impact on the accuracy of the solution. We have also applied these ideas to areas where previous computer architecture researches have mostly neglected: a) the revenue and profit implications of design decisions b) the user satisfaction during the runtime of an application.

#### 1.2. Organization

The rest of the dissertation continues as follows: Chapter 2 provides related work in the area of benchmarking, data mining and applications of data mining to computer architecture research. First, in Chapter 3 we show why we need a new benchmarking suit and then introduce the MineBench benchmark in detail. Then Chapter 4 describes the architectural characteristics of the benchmark for single and multiprocessor cases. Optimization of data mining workloads using hardware accelerators are presented in Chapter 5. Chapter 6 continues with our related work in the embedded data mining systems area. Chapter 7 shows an example of how data mining applications can be used to tackle the complex design space problem in computer architecture. Then, data mining models are used to present the strong relation between the processor properties and its price in Chapter 8. Chapter 9 is the last example where data mining was used to learn per user satisfaction for different applications and leverage it to save power. Our conclusion is presented in Chapter 10 and followed by future work.

#### CHAPTER 2

### Literature Survey

Benchmarks play a major role in all domains. SPEC [103] benchmarks have been well accepted and used by several chip makers and researchers to measure the effectiveness of their designs. Other fields have popular benchmarking suites designed for the specific application domain: TPC [107] for database systems, SPLASH [113] for parallel architectures, and MediaBench [67] for media and communication processors. We understand the indispensable need for a data mining benchmark suite since there are currently no mechanisms to review data mining algorithms and the systems that run them.

#### 2.1. Analysis, Characterization and Design of Data Mining Applications

Performance characterization studies similar to ours have been previously performed for database workloads [48, 62], with some of these efforts specifically targeting SMP machines [92, 106]. Performance characterization of individual data mining algorithms have been done [20, 64], where the authors focus on the memory and cache behavior of a decision tree induction program.

Characterization and optimization of data-mining workloads is a relatively new field. Our work builds on prior effort in analyzing the performance scalability of bioinformatics workloads performed by researchers at Intel Corporation [26]. As it will be described in the following Chapter 3, we incorporate their bioinformatics workloads into our MineBench suite, and where applicable, make direct comparisons between their results and our own. However, MineBench is more generic and covers a wider spectrum than the bioinformatics applications previously studied [26]. Jaleel et al. examine the last-level cache performance of these bioinfomatics applications [58].

The bioinformatics applications presented in MineBench differ from other recentlydeveloped bioinformatics benchmark suites. BioInfoMark [68], BioBench [3], BioSplash [9], and BioPerf [8] all contain several applications in common, including *Blast*, *FASTA*, *Clustalw*, and *Hmmer*. BioInfoMark and BioBench contain only serial workloads. In BioPerf, a few applications have been parallelized, unlike MineBench which contains full fledged OpenMP [18] parallelized codes of all bioinformatics workloads. Srinivasan et al. [102] explore the effects of cache misses and algorithmic optimizations on performance for one of the applications in MineBench (SVM-RFE), while our work investigates several architectural features of data mining applications. Sanchez et al. [94] perform architectural analysis of a commonly used biological sequence alignment algorithm, whereas we attempt to characterize a variety of data mining algorithms used in biological applications.

There has been prior research on hardware implementations of data mining algorithms. In [35] and [112], K-means clustering is implemented using reconfigurable hardware. Baker and Prasanna [11] use FPGAs to implement and accelerate the Apriori [2] algorithm, a popular association rule mining technique. They develop a scalable systolic array architecture to efficiently carry out the set operations, and use a "systolic injection" method for efficiently reporting unpredicted results to a controller. In [10], the same authors use a bitmapped CAM architecture implementation on an FPGA platform to achieve significant speedups over software implementations of the Apriori algorithm. Compared to our designs, these implementations target different classes of data mining algorithms. We have also looked at Graphical Processing Units (GPUs) as the new medium of hardware acceleration. Barrachina et al. [14, 13] evaluate the performance of Level 3 operations in CUBLAS. They also present algorithms to compute the solution of a linear system of equations on a GPU, as well as general techniques to improve their performance. Jung [57] presents an efficient algorithm for solving symmetric and positive definite linear systems using the GPU. Govindaraju et al. [45] present algorithms for performing fast computation of several common database operations, e.g., conjugate selections, aggregations, and semi-linear queries, on commodity graphics hardware. Volkov [109] presents dense linear algebra and Nukada et. al. [82] present 3-D FFT on NVIDIA GPUs. As these studies show that GPUs can be used for various application domains, they do not specifically focus on data mining algorithms, which is the target of our work.

Our approach in the embedded data mining work is similar to work done in the Digital Signal Processing [75, 93] domain. In [93], the authors have used MATLAB to semiautomate conversion of floating point MATLAB programs into fixed point programs, to be mapped onto FPGA hardware. Their implementation tries to minimize hardware resources, while constraining quantization errors within a specific limit. Currently our fixed point conversion is done manually. However, we support varying precisions and do not perform input scaling transformations. In [24], an implementation of sensory stream data mining using fixed point arithmetic has been described. The authors in [40] have used fixed point arithmetic with pre-scaling to obtain decent speedups for artificial neural networks used in natural language processing. Several data mining algorithms have been previously implemented on FPGAs [12, 118, 36, 24]. In [12], the Apriori algorithm, which is nearly pure integer arithmetic, has been implemented on hardware. In [36], algorithmic transformations on K-means clustering have been studied for reconfigurable logic. In [65], the authors have implemented Basic Local Alignment Search Tool (BLAST) by using a low level FPGA near the disk drives, and then using a traditional processor.

#### 2.2. Applications of Data Mining to Computer Architecture

There have been numerous works done in the area of design space exploration. Eyerman et al. [37] uses a different heuristics to model the shape of the design space of superscalar out-of-order processor. Ipek et al. [55] use artificial neural networks to predict the performance of memory, processor, and CMP design spaces. However, in their work, they have only used simulation results to create their design space for SPEC2000 applications, and used neural networks with cross validation to calculate their prediction accuracy. Meanwhile, Lee et al. [66] use regression models to predict performance and power usage of the applications found in the SPECjbb and SPEC2000 benchmarks. As in the previous reference, the data points are created using simulations. Kahn et al. [63] uses predictive modeling, a machine learning technique to tackle the problem of accurately predicting the behavior of unseen configurations in CMP environment. Ghosh et al. [42] have presented an analytical approach to the design space exploration of caches that avoids exhaustive simulation. Their approach uses an analytical model of the cache combined with algorithms to directly and efficiently compute a cache configuration meeting designers' performance constraints. The problem that they are trying to solve (only varying cache size and associativity) is very small compared to the ones that other researchers and we are trying to solve. Dubach et al. [31] has used a combination of linear

regressor models in conjunction with neural networks to create a model that can predict the performance of programs on any microarchitectural configuration with only using 32 further simulations. In our work, we target system performance rather than processor performance. All of these works have based their models on simulation while our results use simulation results as well as already built existing computer systems. The closest work is by Ipek et al. [54], where they use artificial neural networks to predict the performance of SMG2000 applications run on multi-processor systems. The application inputs and the number of processors the application runs on are changed during their analysis. Their accuracy results are around 12.3% when they have 250 data points for training. However, we must point that they also do not perform an estimation of the performance of the systems but rather simulate the execution of an application on one system.

Variability in process technologies, that we have based our work Profit-Aware Cache Architecture, has been extensively studied. There have been several cache redundancy schemes proposed. These techniques have been/could be used to reduce the critical delay of a cache. Victim caches [60] are extra level of caches used to hold blocks evicted from a CPU cache due to a conflict or capacity miss. A substitute cache (SC) storing the slower blocks of the cache is orthogonal to a victim cache, which stores blocks evicted from the cache. Sohi [99] shows that cache redundancy can be used to prevent yield loss, using a similar concept to our proposed SC cache. Ozdemir et al. [87] present microarchitectural schemes that improve the overall chip yield under process variations. The authors have shown how powering down sections of the cache can increase the effective yield. Our work, on the other hand encompasses extra redundancy in L1 caches to facilitate efficient binning and profit maximization. There have been numerous studies analyzing cache resizing for different goals such as minimizing power consumption or increasing performance. Selective Cache Ways by Albonessi [4] is one of the first works in cache resizing and optimizing energy dissipation of the cache. However, to the best of our knowledge no resizing schemes has been applied to alter speed-binning and profit.

Dynamic voltage and frequency scaling (DVFS) is an effective technique for microprocessor energy and power control for most modern processors [21, 44]. Energy efficiency has traditionally been a major concern for mobile computers. Fei, Zhong and Ya [39] propose an energy-aware dynamic software management framework that improves battery utilization for mobile computers. However, this technique is only applicable to highly adaptive mobile applications. Researchers have proposed algorithms based on workload decomposition [27], but these tend to provide power improvements only for memorybound applications. Wu et al. [114] present a design framework for a run-time DVFS optimizer in a general dynamic compilation system. However, none of the previous DVFS techniques consider the user satisfaction prediction. Mallik et al. [73, 74] show that it is possible to utilize user feedback to control a power management scheme, i.e., allow the user to control the performance of the processor directly. However, their system requires constant feedback from the user. Our scheme, correlates to user satisfaction with low level microarchitectural metrics. In addition, we use a learning mechanism to eliminate the user feedback to make long-term feedback unnecessary. Sasaki et al. [95] propose a novel DVFS method based on statistical analysis of performance counters. However, their technique needs compiler support to insert code for performance prediction. Furthermore, their technique does not consider user satisfaction while setting the frequency.

### CHAPTER 3

## MineBench

The increasing performance gap between data mining systems and algorithms may be bridged by a two phased approach: a thorough understanding of the system characteristics and bottlenecks of data mining applications, followed by design of novel computer

| Application Category Description |                |                                                                     |  |  |

|----------------------------------|----------------|---------------------------------------------------------------------|--|--|

| ScalParC                         | Classification | Decision tree classification                                        |  |  |

| Naive Bayesian                   | Classification | Simple statistical classifier                                       |  |  |

| K-means                          | Clustering     | Mean-based data partitioning method                                 |  |  |

| Fuzzy K-means                    | Clustering     | Fuzzy logic-based data partitioning method                          |  |  |

| HOP                              | Clustering     | Density-based grouping method                                       |  |  |

| BIRCH                            | Clustering     | Hierarchical clustering method                                      |  |  |

| Eclat                            | ARM            | Vertical database, Lattice transversal<br>techniques used           |  |  |

| Apriori                          | ARM            | Horizontal database, level-wise mining based on<br>Apriori property |  |  |

| Utility                          | ARM            | Utility-based association rule mining                               |  |  |

| SNP                              | Classification | Hill-climbing search method for DNA<br>dependency extraction        |  |  |

| GeneNet                          | Classification | Gene relationship extraction using<br>microarray-based method       |  |  |

| SEMPHY                           | Classification | Gene sequencing using phylogenetic tree-based method                |  |  |

| Rsearch                          | Classification | RNA sequence search using stochastic Context-Free<br>Grammars       |  |  |

| SVM-RFE                          | Classification | Gene expression classifier using recursive feature elimination      |  |  |

| PLSA                             | Optimization   | DNA sequence alignment using Smith-Waterman<br>optimization method  |  |  |

Table 3.1. Overview of the MineBench data mining benchmark suite

systems to cater to the primary demands of data mining workloads. We address this issue in this work by investigating the execution of data mining applications on a sharedmemory parallel (SMP) machine. We first establish a benchmarking suite of applications that we call MineBench, which encompasses many algorithms commonly found in data mining. We then analyze the architectural properties of these applications to investigate the performance bottlenecks associated with them. The fifteen applications that currently comprise MineBench are listed in Table 3.1, and are described in more detail in Section 3.2.

#### 3.1. Need for a New Benchmarking Suite and Uniqueness

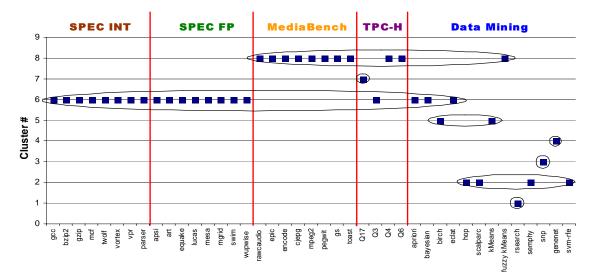

A new benchmarking suite is highly motivated if applications in a domain exhibit distinctive characteristics. In this section, we focus on the uniqueness of data mining applications, as compared to other application domains. We compare the architectural characteristics of applications across various benchmark suites. Specifically, data mining applications are compared against compute intensive applications, multimedia applications, streaming applications and database applications to identify the core differences. In this analysis, we used a variety of application suites including integer application benchmarks (SPEC INT from SPEC CPU2000 [103]), floating point application benchmarks (SPEC FP from SPEC CPU2000), multimedia application benchmarks (MediaBench [67]) and decision support application benchmarks (TPC-H from Transaction Processing Council [107]). We perform statistical analysis on 19 architectural characteristics (such as branch instructions retired, L1 and L2 cache accesses, etc.) of the applications and use this information to identify the core differences. Specifically, we monitor the performance counters of each application during execution using profiling tools, and obtain their individual characteristics. The experimental framework is identical to the one described in Chapter 4. The applications are then categorized using a K-means based approach, which clusters the applications with similar characteristics together. A similar approach has been used to identify a representative workload of SPEC benchmarks [33]. Figure 3.1 shows the scatter plot of the final configuration obtained from the results of the clustering method. Applications belonging to the SPEC INT, SPEC FP, TPC-H, and MediaBench benchmark suites are assigned to respective clusters. However, it can be seen that data mining applications stand out from other benchmark suites: they are scattered across several clusters. Although some of the data mining applications share characteristics with other application domains, they mostly exhibit unique characteristics. Another important property of the clustering results is the large variation within data mining applications. Although most of the applications in other benchmarking suites fall into one cluster, data mining applications fall into seven different clusters. This shows the large variation of characteristics observed in data mining applications. Overall, this analysis highlights the need for a data mining benchmark consisting of various representative algorithms that cover the spectrum of data mining application domains.

Table 3.2 shows the distinct architectural characteristics of data mining applications as compared to other applications. One key attribute that signifies the uniqueness of data mining applications is the number of data references per instruction retired. For data mining applications, this rate is 1.103, whereas for other applications, it is significantly less. The number of bus accesses originating from the processor to the memory (per

Figure 3.1. Classification of data mining, SPEC INT, SPEC FP, Media-Bench and TPC-H benchmark applications based on their characteristics. A K-means based clustering algorithm was used for this classification. Data mining applications tend to form unique clusters.

Table 3.2. Comparison of data mining application with other benchmark applications

|                         |         | Benchmark of Applications |            |        |              |

|-------------------------|---------|---------------------------|------------|--------|--------------|

| $Parameter^{\dagger}$   | SPECINT | SPECFP                    | MediaBench | TPC-H  | NU-MineBench |

| Data References         | 0.81    | 0.55                      | 0.56       | 0.48   | 1.10         |

| Bus Accesses            | 0.030   | 0.034                     | 0.002      | 0.010  | 0.037        |

| Instruction Decodes     | 1.17    | 1.02                      | 1.28       | 1.08   | 0.78         |

| Resource Related Stalls | 0.66    | 1.04                      | 0.14       | 0.69   | 0.43         |

| CPI                     | 1.43    | 1.66                      | 1.16       | 1.36   | 1.54         |

| ALU Operations          | 0.25    | 0.29                      | 0.27       | 0.30   | 0.31         |

| L1 Misses               | 0.023   | 0.008                     | 0.010      | 0.029  | 0.016        |

| L2 Misses               | 0.003   | 0.003                     | 0.0004     | 0.002  | 0.006        |

| Branches                | 0.13    | 0.03                      | 0.16       | 0.11   | 0.14         |

| Branch Mispredictions   | 0.009   | 0.0008                    | 0.016      | 0.0006 | 0.006        |

<sup>†</sup> The numbers shown here for the parameters are values per instruction

instruction retired) verify the frequency of data access of data mining applications. These results solidify the intuition that data mining is data-intensive by nature.

The L2 miss rates are considerably high for data mining applications. The reason for this is the inherent streaming nature of data retrieval, which does not provide enough opportunities for data reuse. This indicates that current memory hierarchy is insufficient for data mining applications. It should be noted that the number of branch instructions (and the branch mispredictions) are typically low for data mining applications, which highlights yet another unique behavior of data mining applications.

Another important difference is the fraction of total instruction decodes to the instructions retired. This measure identifies the instruction efficiency of a processor. In our case, the results indicate that data mining applications are efficiently handled by the processor. The reason for this value being less than one is the use of complex SSE2 instructions. Resource related stalls comprises of the delay that incurs from the contention of various processor resources, which include register renaming buffer entries, memory buffer entries, and also the penalty that occurs during a branch misprediction recovery. The number of ALU operations per instruction retired is also surprisingly high for data mining applications, which indicates the extensive amount of computations performed in data mining applications. Therefore, data mining applications are computation-intensive in addition to being data-intensive.

What makes the data mining applications unique is this combination of high data rates combined with high computation power requirements. Such a behavior is clearly not seen in other benchmark suites. In addition, data mining applications tend to oscillate between data and compute phases, making the current processors and architectural optimizations mostly inadequate.

#### 3.2. Benchmark Suite Overview

MineBench contains fifteen representative data mining workloads from various categories. The workloads chosen represent the heterogeneity of algorithms and methods used in data mining. Applications from clustering, classification, association rule mining and optimization categories are included in MineBench. The codes are full fledged implementations of entire data mining applications, as opposed to stand-alone algorithmic kernels. We provide OpenMP parallelized codes for twelve of the fifteen applications. An important aspect of data mining applications are the data sets used. For most of the applications, we provide three categories of data sets with varying sizes: small, medium, and large. In addition, we provide source code, information for compiling the applications using various compilers, and command line arguments for all of the applications.

#### 3.2.1. Classification Workloads

A classification problem has an input dataset called the training set, which consists of example records with a number of attributes. The objective of a classification algorithm is to use this training dataset to build a model such that the model can be used to assign unclassified records into one of the defined classes [47].

ScalParC is an efficient and scalable variation of decision tree classification [59]. The decision tree model is built by recursively splitting the training dataset based on an optimality criterion until all records belonging to each of the partitions bear the same class label. Decision tree based models are relatively inexpensive to construct, easy to interpret and easy to integrate with commercial database systems. ScalParC uses a parallel hashing paradigm to achieve scalability during the splitting phase. This approach makes it scalable in both runtime and memory requirements.

The *Naive Bayesian* classifier [**30**], a simple statistical classifier, uses an input training dataset to build a predictive model (containing classes of records) such that the model can

be used to assign unclassified records into one of the defined classes. Naive Bayes classifiers are based on probability models that incorporate strong independence assumptions which often have no bearing in reality, hence the term "naive". They exhibit high accuracy and speed when applied to large databases.

Single nucleotide polymorphisms (SNPs), are DNA sequence variations that occur when a single nucleotide is altered in a genome sequence. Understanding the importance of the many recently identified SNPs in human genes has become a primary goal of human genetics. The *SNP* [26] benchmark uses the hill climbing search method, which selects an initial starting point (an initial Bayesian Network structure) and searches that point's nearest neighbors. The neighbor that has the highest score is then made the new current point. This procedure iterates until it reaches a local maximum score.

Recent advances in DNA microarray technologies have made it possible to measure expression patterns of all the genes in an organism, thereby necessitating algorithms that are able to handle thousands of variables simultaneously. By representing each gene as a variable of a Bayesian Network (BN), the gene expression data analysis problem can be formulated as a BN structure learning problem. *GeneNet* [26] uses a similar hill climbing algorithm as in SNP, the main difference being that the input data is more complex, requiring much additional computation during the learning process. Moreover, unlike the SNP application, the number of variables runs into thousands, but only hundreds of training cases are available. GeneNet has been parallelized using a node level parallelization paradigm, where in each step, the nodes of the BN are distributed to different processors.

SEMPHY [26] is a structure learning algorithm that is based on phylogenetic trees. Phylogenetic trees represent the genetic relationship of a species, with closely related species placed in nearby branches. Phylogenetic tree inference is a high performance computing problem as biological data size increases exponentially. SEMPHY uses the structural expectation maximization algorithm, to efficiently search for maximum likelihood phylogenetic trees. The computation in SEMPHY scales quadratically with the input data size, necessitating parallelization. The computation intensive kernels in the algorithm are identified and parallelized using OpenMP.

Typically, RNA sequencing problems involve searching the gene database for homologous RNA sequences. *Rsearch* [26] uses a grammar-based approach to achieve this goal. Stochastic context-free grammars are used to build and represent a single RNA sequence, and a local alignment algorithm is used to search the database for homologous RNAs. Rsearch is parallelized using a dynamic load-balancing mechanism based on partitioning the variable length database sequence to fixed length chunks, with specific domain knowledge.

SVM-RFE [26], or Support Vector Machines - Recursive Feature Elimination, is a feature selection method. SVM-RFE is used extensively in disease finding (gene expression problem). The selection is obtained by a recursive feature elimination process - at each RFE step, a gene is discarded from the active variables of a SVM classification model, according to some support criteria. Vector multiplication is the computation intensive kernel of SVM-RFE, and data parallelism using OpenMP, is utilized to parallelize the algorithm.

#### 3.2.2. Clustering Workloads

Clustering is the process of discovering the groups of similar objects from a database to characterize the underlying data distribution [47]. It has wide applications in market or customer segmentation, pattern recognition, and spatial data analysis.

The first clustering application in MineBench is *K*-means [71]. K-means represents a cluster by the mean value of all objects contained in it. Given the user-provided parameter k, the initial k cluster centers are randomly selected from the database. Then, each object is assigned a nearest cluster center based on a similarity function. Once the new assignments are completed, new centers are found by finding the mean of all the objects in each cluster. This process is repeated until some convergence criteria is met. K-means tries to minimize the total intra-cluster variance.

The clusters provided by the K-means algorithm are sometimes called "hard" clusters, since any data object either is or is not a member of a particular cluster. The *Fuzzy K-means* algorithm [16] relaxes this condition by assuming that a data object can have a degree of membership in each cluster. Compared to the similarity function used in K-means, the calculation for fuzzy membership results in a higher computational cost. However, the flexibility of assigning objects to multiple clusters might be necessary to generate better clustering qualities. Both K-means and Fuzzy K-means are parallelized by distributing the input objects among the processors. At the end of each iteration, extra communication is necessary to synchronize the clustering process.

HOP [34], originally proposed in astrophysics, is a typical density-based clustering method. After assigning an estimation of the density for each particle, HOP associates each particle with its densest neighbor. The assignment process continues until the densest neighbor of a particle is itself. All particles reaching the same such particle are clustered into the same group. The advantage of HOP over other density based clustering methods is that it is spatially adaptive, coordinate-free and numerically straightforward. HOP is parallelized using a three dimensional KD tree data structure, which allows each thread to process only a subset of the particles, thereby reducing communication cost significantly.

*BIRCH* [119] is an incremental and hierarchical clustering algorithm for large databases. It employs a hierarchical tree to represent the closeness of data objects. BIRCH scans the database to build a clustering-feature (CF) tree to summarize the cluster representation. For a large database, BIRCH can achieve good performance and scalability. It is also effective for incremental clustering of incoming data objects, or when an input data stream has to be clustered.

#### 3.2.3. ARM Workloads

The goal of Association Rule Mining (ARM) is to find interesting relationships hidden in large data sets. More specifically, it attempts to find the set of all subsets of items or attributes that frequently occur in database records [47]. In addition, the uncovered relationships can be represented in the form of association rules, which state how a given subset of items influence the presence of another subset.

Apriori [2] is the first ARM algorithm that pioneered the use of support-based pruning to systematically control the exponential growth of the search space. It is a level-wise algorithm that employs a generate-and-test strategy for finding frequent itemsets. It is based on the property that all non-empty subsets of a frequent itemset must all be frequent (the so-called "Apriori" property). For determining frequent items in a fast manner, the algorithm uses a hash tree to store candidate itemsets. Note: This hash tree has item sets at the leaves and hash tables at internal nodes. The Apriori algorithm is parallelized by distributing chunks of the input data among the processors. The master processor then gathers the local candidate itemsets, and generates globally frequent itemsets.

Utility mining [69] is another association rule-based mining technique where the assumption of uniformity among items is discarded. Higher "utility" itemsets are identified from a database by considering different values for individual items. The goal of utility mining is to restrict the size of the candidate set so as to simplify the total number of computations required to calculate the value of items. It uses the "transaction-weighted downward closure property" to prune the search space. The parallelization paradigm applied to Utility mining is the same as in Apriori, described above.

*Eclat* [116] uses a vertical database format. It can determine the support of any kitemset by simply intersecting the id-list of the first two (k-1)-length subsets that share a common prefix. It breaks the search space into small, independent, and manageable chunks. Efficient lattice traversal techniques are used to identify all the true maximal frequent itemsets.

#### 3.2.4. Optimization Workloads

Sequence alignment is an important problem in bioinformatics used to align DNA, RNA or protein primary sequences so as to emphasize their regions of similarity. It is used to identify the similar and diverged regions between two sequences, which may indicate functional and evolutionary relationships between them. *PLSA* [26] uses a dynamic programming approach to solve this sequence matching problem. It is based on the algorithm proposed by Smith and Waterman, which uses the local alignment to find the longest common substring in sequences. PLSA uses special data structures to intelligently segment the whole sequence alignment problem into several independent subproblems, which dramatically reduce the computation necessary, thus providing more parallelism than previous sequence alignment algorithms.

## 3.2.5. Input Datasets

Input data is an integral part of data mining applications. The data used in our experiments are either real-world data obtained from various fields or widely-accepted synthetic data generated using existing tools that are used in scientific and statistical simulations. During evaluation, multiple data sizes were used to investigate the characteristics of the MineBench applications. For the non-bioinformatics applications, the input datasets were classified into three different sizes: small, medium, and large. For the ScalParC and Naive Bayesian applications, three synthetic datasets were generated by the IBM Quest data generator [1]. Apriori also uses three synthetic datasets from the IBM Quest data generator with a varying number of transactions, average transaction size, and average size of the maximal large itemsets. For HOP and Birch, three sets of real data were extracted from a cosmology application, ENZO [81], each having 61440 particles, 491520 particles and 3932160 particles.

A section of the real image database distributed by Corel Corporation is used for K-means and Fuzzy K-means. This database consists of 17695 scenery pictures. Each picture is represented by two features: color and edge. The color feature is a vector of 9 floating points while the edge feature is a vector of size 18. Since the clustering quality of K-means methods highly depends on the input parameter k, both K-means were executed with 10 different k values ranging from 4 to 13. Utility mining uses both real as well as synthetic datasets. The synthetic data consists of two databases generated using the IBM Quest data generator. The first synthetic dataset is a dense database, where the average transaction size is 10; the other is a relatively sparse database, where average transaction size is 20. The average size of the potentially frequent itemsets is 6 in both sets of databases. In both sets of databases, the number of transactions varies from 1000K to 8000K and the number of items varies from 1K to 8K. The real dataset consists of only one database of size 73MB, where the average transaction length is 7.2.

Bioinformatics applications use datasets obtained from different biological databases. For the bioinformatics applications, the datasets were provided by Intel [26]. SNP uses the Human Genic Bi-Alletic Sequences (HGBASE) database [22] containing 616,179 SNPs sequences. For GeneNet, the microarray data used for this study is assembled from [100]; they are the most popular cell cycle data of Yeast. SEMPHY considers three datasets from the Pfam database [15]. The software and the corresponding dataset for Rsearch were obtained from [96]. The experiments use the sequence mir-40.stk with the length of 97 to search a part of database Yeastdb.fa with size of 100KB. SVM-RFE uses a benchmark microarray dataset on ovarian cancer [5]. This dataset contains 253 (tissue samples)  $\times$  15154 (genes) expression values, including 91 control and 162 ovarian cancer tissues with early stage cancer samples. For PLSA, nucleotides ranging in length from 30K to 900K are chosen as test sequences. Since true sequences can seldom satisfy this specific size, some artificial sequences were used in the experiments [26]. To make the experiments more comprehensive, several real DNA sequences were also chosen from a test suite provided by the bioinformatics group at Penn State University. The longest sequence pair used here is named TCR where the human sequence is 319,030 bp long and the mouse sequence is 305,636 bp long.

## CHAPTER 4

# Architectural Characterization

In this section, we consider the applications in our MineBench suite, and distinguish the characteristics that make each application unique from both the algorithmic and the system perspective. We chose an Intel IA-32 multiprocessor platform for evaluation purposes. Our setup consists of an Intel Xeon 8-way Shared Memory Parallel (SMP) machine running Red Hat Advanced Server 2.1. The system has 4 GB of shared memory. Each processor has a 16 KB non-blocking, integrated L1 cache and a 1024 KB L2 cache.

For our experiments, we use the VTune Performance Analyzer [53] for profiling the functions within our applications, and for measuring the execution times. Using the VTune counters, we monitor a wide assortment of performance metrics: execution time, communication and synchronization complexity, memory behavior, and Instructions per Cycle (IPC) statistics. Each application was compiled with version 7.1 of the Intel C++ compiler for Linux.

#### 4.1. Execution Time and Scalability

In Table 4.1, we present the total number of instructions executed across all processors along with the size of the executables. We can see that these benchmarks execute from tens of billions to thousands of billions of instructions. As the number of processors increases, the number of instructions executed is expected to increase due to the overhead of parallelization (locks, communication, synchronization etc.). However we observe that

| Application    | Instruction Count (billions) |              |              |              | Size (kB) |

|----------------|------------------------------|--------------|--------------|--------------|-----------|

| Application    | 1 Processor                  | 2 Processors | 4 Processors | 8 Processors | Size (KD) |

| ScalParC       | 23.664                       | 24.817       | 25.550       | 27.283       | 154       |

| Naive Bayesian | 23.981                       | N/A          | N/A          | N/A          | 207       |

| K-means        | 53.776                       | 54.269       | 59.243       | 77.026       | 154       |

| Fuzzy K-means  | 447.039                      | 450.930      | 477.659      | 564.280      | 154       |

| HOP            | 30.297                       | 26.920       | 26.007       | 26.902       | 211       |

| BIRCH          | 15.180                       | N/A          | N/A          | N/A          | 609       |

| Apriori        | 42.328                       | 42.608       | 43.720       | 47.182       | 847       |

| Eclat          | 15.643                       | N/A          | N/A          | N/A          | 2169      |

| Utility        | 13.460                       | 19.902       | 20.757       | 22.473       | 853       |

| SNP            | 429.703                      | 299.960      | 267.596      | 241.680      | 14016     |

| GeneNet        | 2,244.470                    | 2,263.410    | 2,307.663    | 2,415.428    | 13636     |

| SEMPHY         | 2,344.533                    | 2,396.901    | 1,966.273    | 2,049.658    | 7991      |

| Rsearch        | 1,825.317                    | 1,811.043    | 1,789.055    | 1,772.200    | 676       |

| SVM-RFE        | 51.370                       | 55.249       | 63.053       | 82.385       | 1336      |

| PLSA           | 4,460.823                    | 4,526.160    | 4,080.610    | 4,001.675    | 836       |

Table 4.1. MineBench executable profiles

in some of the applications, instructions retired decreases as the number of processors increases. This may happen when the convergence criteria is reached at an earlier stage during execution of the parallel application. In our study, the usage of Vtune Performance Analyzer enables us to examine the characteristics of program execution across all execution phases, something that would not be feasible using simulation for applications of this size.

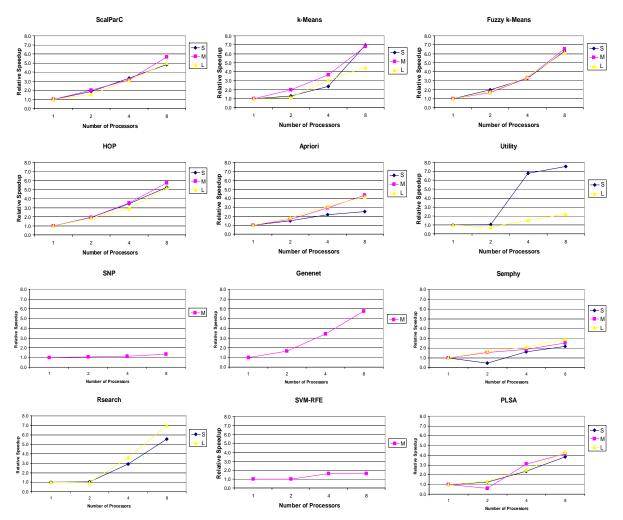

Figure 4.1 shows the benchmark application execution speedups when running on multiple processors. The performance numbers for the 2-processor case shows some trivial performance improvement for clustering and ARM workloads, while most of the remaining workloads perform slightly better or worse than the serial case. On the other hand, several benchmarks show good scalability with higher number of processors. When running on 8 processors, ScalParC executes 4.84 and  $5.64 \times$  faster than the 1 processor case for the

Figure 4.1. Speedups for the MineBench applications

small and large data sets, respectively. The best speedup, 7.55x on 8 processors, is seen in Utility. In this algorithm, data is uniformly distributed to the 8 processors, which are able to work concurrently by accessing only its respective data block in memory, synchronizing only occasionally. Rsearch and K-means follow Utility in terms of achieved speedups. In general, it can be observed that clustering algorithms show better scalability than the remainder of the applications. The underlying reason for this observation is the highly parallelizable distance calculation routine, which is common to the clustering algorithms. The worst scalability is observed for SNP and SVM-RFE. For SVM-RFE, the problem arises due to unnecessary communication problems and locking of memory structures. This redundant locking is done to ensure the code works on distributed and shared memory machines.

For the Utility mining application, the small dataset represents real data collected from a grocery store. The large dataset has been created by the IBM Quest data generator. Both of the datasets contain a nearly equal number of transactions and items. However, the speedups for these two datasets differ widely. Particularly, the application achieves 7.55x speed-up for the small and 2.23x speed-up for the large datasets when executed on 8 processors. When the most time consuming functions are examined, it is seen that the program spends approximately 30% and 50% of the total execution time in the serial database read function, respectively. The change in the time of this serial segment causes the scalability problems for the large dataset.

Intel researchers have done similar analysis for the performance scalability of the bioinformatics workloads [26]. When the above presented results are compared to their results, Genenet, Semphy, Rsearch, and PLSA show very similar scalability trends. However the results are very different for SNP and SVM-RFE, where they are able to achieve close to linear speedup until 8 processors and super-linear speedup for 16 processors. The explanation given for this super-linearity is that Intel's system is composed of a 16-way shared memory machine, which has a large L3 cache and Cell-sharing L4 caches (4 processors grouped together) that are interconnected with each other through the crossbar. Specific optimizations have been applied to these codes targeting their system. However, other researchers from Intel have shown that SVM-RFE reaches only 2.3x speed-up on their

4-way shared memory machine [102]. This is a sign that architecture plays an important role in the performance of these applications.

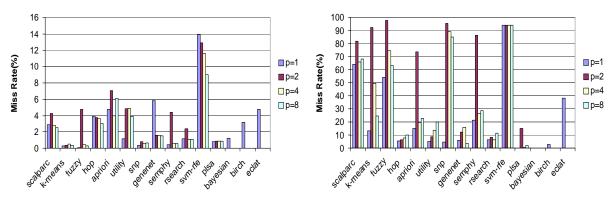

#### 4.2. Memory Hierarchy Behavior

It is well known that memory hierarchy is a major performance bottleneck in modern computing systems. It is therefore necessary to understand the memory hierarchy behavior of data mining applications before attempting to improve performance. Figures 4.2 and 4.3 summarize the results obtained for memory hierarchy behavior (level 1 data, and level 2 caches, respectively) over 1, 2, 4 and 8 processor runs on medium sized datasets, wherever applicable. We notice several interesting aspects of memory behavior from these results. First, though L1 data cache miss rates are usually small, applications are drastically different in their L1 data cache behavior. We can separate the applications into two categories: those that have very small L1 data miss rates (less than 1.5%), and those that have larger miss rates (2-14%). It is also interesting to note that even in applications with low L1 data miss rates, in many cases, the 2-processor run yields much higher cache misses than the other runs. In general, we see that as the number of processors increase, L1 data cache miss rates decrease. This is due to the fact that multiple processors are working on a smaller chunk of data. Note that, for some applications, the miss rates are independent of the number of processors. In these applications, most misses are caused by cold and invalidation misses, hence they are largely unaffected by the number of processors. We also studied the L1 instruction cache miss rates. In general the L1 instruction cache miss rates are very low (on average 0.11%). This is due to the fact that the applications are relatively small in size and the instructions are able to fit into the L1 cache easily. More importantly, most of the execution in these applications are in the relatively small number of frequently executed kernels. Since the miss rates during the execution of these kernels are low, the overall instruction cache misses remain low. We have not observed much variance of instruction miss rate while going from 1 processors to 8 processors, because these applications, in general, use data parallelization concepts.

An analysis of the L2 cache behavior was also carried out and yielded several unique characteristics. It is seen that L2 cache miss rates are many times greater than their corresponding L1 counterparts. Generally, there are two reasons for such high L2 miss rates. First, for some applications the L1 miss rates are extremely small, as a result most of the L2 accesses result in cold misses. Second, several applications work on very large datasets in a streaming fashion. Overall, the SVM-RFE benchmark had the worst L2 cache miss rates. Combined with its low L1 efficiency, approximately 8.44% of all data references incur costly off-chip memory access, thus yielding a very low IPC for this application. Another interesting observation is that in majority of the applications, the L2 miss rate for the 2 processor case is highest. One reason for this kind of behavior is that the data distribution is random as dynamic scheduling is used for parallelization in some of the applications. In dynamic schemes, the processor gets assigned a new block of data in a random fashion as it becomes available. Hence the data gets distributed to multiple caches in a random fashion, which increases the likelihood of not exploiting temporal or spatial data locality.

### 4.3. Instruction Efficiency

We also studied the instruction efficiency using the counters profiled by VTune. Particularly, we measure the branch misprediction rates, the fraction of floating-point instructions, resource related stalls (stalls caused by register renaming buffer entries, memory buffer entries, and branch misprediction recovery), and the Instructions per Cycle (IPC) values observed. These results are summarized in Figures 4.4, 4.5, 4.6, and 4.7, respectively.

In general, the branch prediction performs very well, with an average misprediction rate of 3.27% for the 15 applications. This is mostly due to the fact that the applications have small kernels which consist of loops that execute for very large number of iterations. Also, the applications are parallelized using OpenMP, which is good at analyzing large loops to extract data parallelism in an efficient way. The highest branch misprediction rate is observed for the HOP and Apriori applications. In both cases, this is partly due to the paradigm applied to parallelize the algorithms. In these two applications, the dataset is read in parallel and each processor works on local data for the most part, only synchronizing occasionally. The application does not have a concise kernel that is executed repeatedly, hence the branch misprediction increases. It is also seen that, in most applications, the branch misprediction rate decreases as the degree of parallelism increases.